# EMBEDDED SYSTEMS VOLUME 5 NUMBER 5 JULY/AUG 2009

INCLUDING

### Chris A. Ciufo

Throwing a Lasko around serial ports

### Field Intelligence

Reflective memory hastens shared access

### Mil Tech Insider

COTS vendors speed FPGA development

### **Legacy Software Migration**

Legacy enhancement: Nightmare or dream?

mobil Also: Net-centric operations rely on COTS

Supplement inside

MIL/COTS DIGEST

Focus on VME

Pentek delivers board and system-level SDR products that include digital downconverters, upconverters and transceivers. Since all of these products are FPGA-based, Pentek offers powerful factory-installed IP cores plus the GateFlow FPGA Design Kit for custom development. These software radio solutions are perfect for applications in communications, SIGINT, radar, direction finding and many more.

Let Pentek help you get your software radio systems out of the nest on time!

Call 201-818-5900 or go to www.pentek.com/go/messdregg for your FREE Software Defined Radio Handbook, technical datasheets and to request pricing.

- XMC/PMC, PCI, PCIe, VME/VXS, cPCI

- · Over 150 software radio modules

- Up to 512 channels of DDC per slot

- New 200 MHz, 16-bit A/Ds

- FPGA-installed SDR IP cores

- Recording systems with rates up to 800 MB/sec

# Annapolis Micro Systems The FPGA Systems Performance Leader

# WILDSTAR 5 for IBM Blade The Perfect Blend of Processors and FPGAs

Fully Integrated into IBM Blade Management System

Abundant Power and Cooling Ensure Maximum Performance

Made in the USA

### **Ultimate Modularity**

From 2 to 8 Virtex 5 FPGA/Memory Modules Input / Output Modules Include: Quad 130 MSps thru Quad 500 MSps A/D 1.5 GSps thru 2.2 GSps, Quad 600 MSps A/D Dual 1.5 GSps thru 4.0 GSps D/A Infiniband, 10 G Ethernet, FC4, SFPDP

Direct Seamless Connections with no Data Reduction

Between External Sensors and FPGAs

Between FPGAs and Processors over IB or 10GE Backplane

Between FPGAs and Standard Output Modules

190 Admiral Cochrane Drive, Suite 130, Annapolis, Maryland USA 21401 wfinfo@annapmicro.com (410) 841-2514 www.annapmicro.com

# EMBEDDED SYSTEM

July/August 2009 Volume 5 Number 5

### COLUMNS

### Field Intelligence

Reflective memory speeds shared access applications

By Duncan Young

### Mil Tech Insider

**COTS vendors speed FPGA development**

By John Wemekamp

### **Legacy Software Migration**

10 Legacy enhancement: Nightmare or dream?

By Mark Pitchford, LDRA

### **Crosshairs Editorial**

42 Throwing a Lasko around serial ports

By Chris A. Ciufo

### DEPARTMENTS

12-13 Daily Briefing: News Snippets

By Sharon Schnakenburg

40-41 Editor's Choice Products

### ON THE COVER:

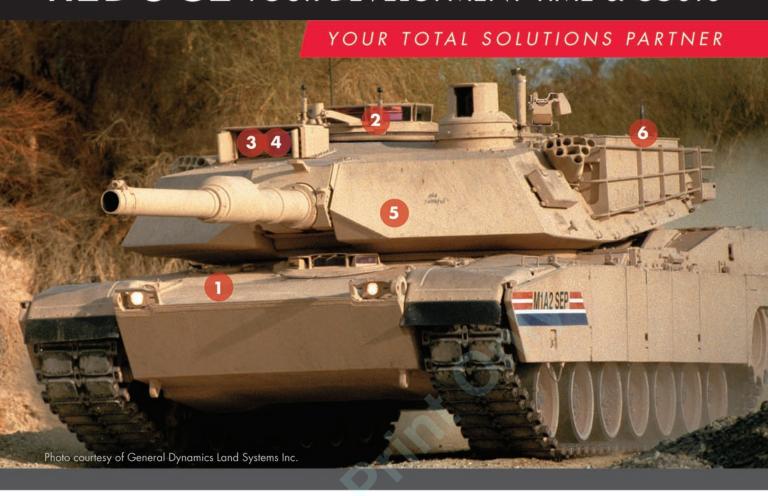

Based on an exclusive interview with General Dynamics, editor Sharon Schnakenburg tells how the Army's WIN-T enables mobile comms via the DoD's Global Information Grid (GIG). General Dynamics has successfully built and tested the largest mobile network of its kind, providing an environment in which commanders at all echelons will have the ability to maneuver anywhere on the battlefield and communicate and collaborate with warfighters, command posts, and analytical centers at remote locations throughout the battlespace. Story on page 18. (Image courtesy of General Dynamics C4 Systems; www.gdc4s.com)

ISSN: Print 1557-3222

All registered brands and trademarks within Military Embedded Systems magazine are the property of their respective owners.

© 2009 OpenSystems Media © 2009 Military Embedded Systems

### Software: VSIPL for radars

Case study: Developing high-performance radar applications using the VSIPL++ API

By Don McCoy, CodeSourcery

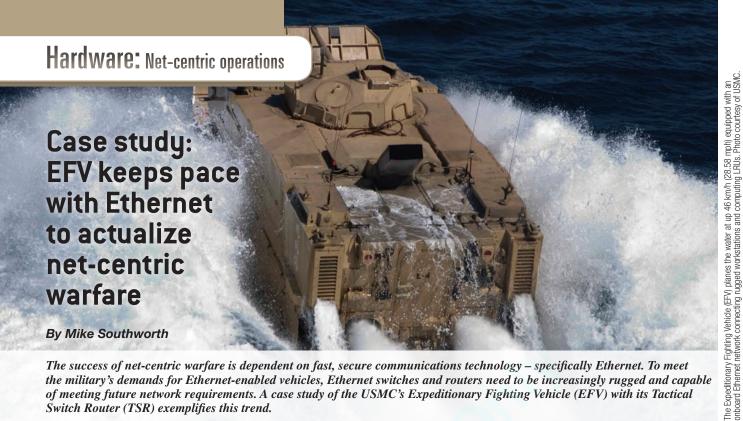

### Hardware: Net-centric operations

18 General Dynamics and WIN-T: Pursuing the GIG

By Sharon Schnakenburg, Associate Editor

Finding the right balance: Deep packet inspection encourages innovation and information sharing while protecting DoD networks

By Kevin Curran, Bivio Networks

Case study: EFV keeps pace with Ethernet to actualize net-centric warfare

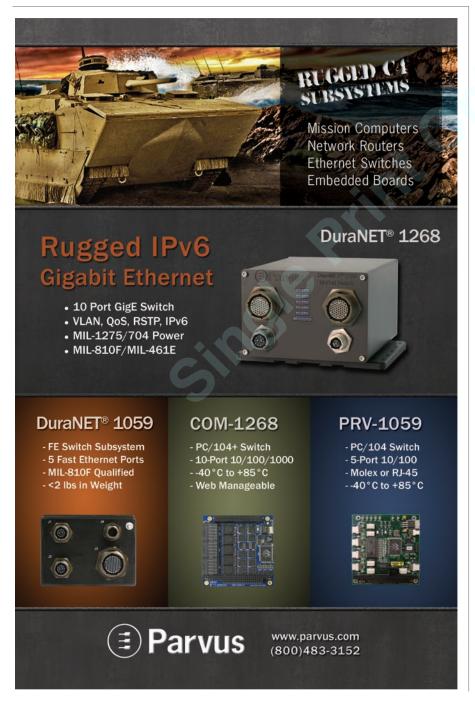

By Mike Southworth, Parvus Corporation

23

Special: VITA 57 thwarts I/O hassles

Adopting VITA 57 (FMC): Reducing FPGA I/O headaches

By Ron Huizen, BittWare

Software: Folding xTCA into VPX

PICMG's xTCA meets VME and VPX head-on

Q&A with Mark Overgaard, Pigeon Point Systems

### **EVENTS**

www.opensystemsmedia.com/events

Embedded Systems Conference – Boston

September 21-24, 2009 • Boston, MA http://esc-boston.techinsightsevents.com

**Intel Developer Forum**

September 22-24, 2009 • San Francisco, CA www.intel.com/idf

### **WEB RESOURCES**

Subscribe to the magazine or E-letter Live industry news • Submit new products

http://submit.opensystemsmedia.com

White papers:

Read: http://whitepapers.opensystemsmedia.com Submit: http://submit.opensystemsmedia.com

### Field Intelligence

## Reflective memory speeds shared access applications

The introduction of network-enabled applications to many defense and aerospace projects allows multiple participants to work cooperatively with shared data. Using file servers and Network Attached Storage (NAS), the applications can access and update the same data sets wherever they might be located on the network. Ethernet is the first choice of network technology for military and commercial/office applications of this type. However, there is a class of applications where Ethernet or other network/fabric technologies are just not fast or deterministic enough. Flight simulators, aircraft simulators, jet engine testing simulators, or war gaming/battlefield simulators are typical examples of complex systems requiring significant amounts of distributed computing power, sometimes spread over quite large distances and sharing large arrays of volatile data in real time. Many of these applications have turned to reflective memory because of its low latency and high degree of determinism.

### Reflective memory principles

The basis of reflective memory operation is its ability to autonomously replicate the contents of one processor's memory to the memory nodes of all other network members. As a processor writes to memory, the location and content are propagated around a network to the same addressable location in all other network memory nodes. It is not necessary for the processor that is writing data into memory to use any protocol for the replication to take place; however, at the system level there is a need for some predetermination of ownership and access rights to locations within memory space. But this allocation is entirely user- or application-dependent. Higher layers of protocol such as semaphores or handshaking can be added, but again, only if required by a particular application's needs.

A typical application for reflective memory might be an aircraft simulator with processing nodes representing sensors, communications subsystems, flight systems, cockpit display systems, and so on. A number of these nodes would be writing data onto the network, which then replicates the data to all the other nodes. For example, a sensor node, such as a weather radar, will generate a stream of data representative of that particular sensor type, varying in real time with the attitude of the aircraft as it flies through the simulation scenario. With many sensor types and many subsystem types feeding data into such a distributed processing application, it is vital that latency and system response mirror the real-world environment for the simulation to be truly representative.

### Low latency

Keys to the success of reflective memory are its low latency and determinism. Using reflective memory, the typical node-to-node propagation time is on the order of 1 microsecond. Thus, in a system of 30 nodes, it would take only 30 microseconds to propagate through the network to all nodes. Data is transferred at rates

up to the available network bandwidth, which can be 170 MBps or more. Achieving the same latency using other network technologies, such as Ethernet, is impossible even using datagram broadcast because of IP protocol overheads, addressing, and memory write times.

### Ring topology

Reflective memory networks use a high-bandwidth, ring topology with commonly used 2.12 Gbaud signaling to move data in dynamically variable packets of 4 to 64 bytes. Such a ring will have its own data transmission protocols and error checking/ recovery mechanisms plus optional managed hubs, if required, to bypass faulty nodes. The network can be easily expanded simply by adding more memory nodes as required. Using fiber as the network media, node-to-node transmission distances up to 300 m using multimode fiber are possible, or up to 10 Km using singlemode fiber. Reflective memory appears as just a block of memory addressed by its host processor via PCI or PCI Express, enabling it to be used in heterogeneous processing systems with many different host and operating system combinations that support PCI or PCI Express. An example of such a reflective memory node with up to 256 MB of SDRAM, suitable for attachment to a host processor via PCI Express, is the PCIE-5565RC from GE Fanuc Intelligent Platforms (Figure 1).

Figure 1 | The PCIE-5565RC reflective memory node from GE Fanuc Intelligent Platforms.

Both large-scale aerospace/industrial simulators and smaller embedded simulators found within battle groups across a number of vehicles can benefit from the speed of response provided by reflective memory. Currently, no other technology offers the same levels of latency and determinism for use in high-performance, widely distributed, shared data processing applications.

To learn more, e-mail Duncan Young at young.duncan1@btinternet.com.

### VME backplanes from the experts:

- · 30 years of experience in development and production

- · Continual next generation technology

- · Numerous variants, individual solutions

- + Professional CAD layout service

Intelligent solutions make the difference

info@hartmann-elektronik.de www.hartmann-electronic.com

# Military EMBEDDED SYSTEMS

**DSP-FPGA.com**

small form factors

OpenSystems media.

**CompactPCI** and Advanced TCA Systems

Embedded COMPUTING

### Military & Aerospace Group

Chris Ciufo, Group Editorial Director cciufo@opensystemsmedia.com

Don Dingee, Contributing Editor ddingee@opensystemsmedia.com

Jennifer Hesse, Senior Associate Editor jhesse@opensystemsmedia.com

Sharon Schnakenburg, Associate Editor sschnakenburg@opensystemsmedia.com

Terri Thorson, Senior Editor (columns) tthorson@opensystemsmedia.com

Monique DeVoe, Copy Editor

Hermann Strass, European Representative hstrass@opensystemsmedia.com

Konrad Witte, Senior Web Developer

Steph Sweet, Creative Director

Joann Toth, Senior Designer

David Diomede, Art Director

Phyllis Thompson

Circulation/Office Manager subscriptions@opensystemsmedia.com

### Sales Group

Dennis Doyle, Senior Account Manager ddoyle@opensystemsmedia.com

Tom Varcie, Senior Account Manager tvarcie@opensystemsmedia.com

Rebecca Barker, Strategic Account Manager rbarker@opensystemsmedia.com

#### Andrea Stabile

Advertising/Marketing Coordinator astabile@opensystemsmedia.com

Christine Long, Digital Content Manager clong@opensystemsmedia.com

### **International Sales**

Dan Aronovic, Account Manager - Israel daronovic@opensystemsmedia.com

Sam Fan, Account Manager - Asia sfan@opensystemsmedia.com

### **Regional Sales Managers**

Ernest Godsey, Central and Mountain States egodsey@opensystemsmedia.com

Barbara Quinlan, Midwest/Southwest bquinlan@opensystemsmedia.com

Denis Seger, Southern California dseger@opensystemsmedia.com

Sydele Starr, Northern California sstarr@opensystemsmedia.com

Ron Taylor, East Coast/Mid Atlantic rtaylor@opensystemsmedia.com

### **Reprints and PDFs**

Nan Lamade 800-259-0470

republish@opensystemsmedia.com

### Editorial/Business Office

16626 E. Avenue of the Fountains, Ste. 203 Fountain Hills, AZ 85268

Tel: 480-967-5581 Fax: 480-837-6466 Website: www.opensystemsmedia.com

Publishers: John Black, Michael Hopper, Wayne Kristoff

Advertiser/Ad title

Vice President Editorial: Rosemary Kristoff

Vice President Marketing & Sales:

Patrick Hopper

phopper@opensystemsmedia.com

Business Manager: Karen Layman

| <b>\</b> | ı uyc  | Auvorusoi/Au uuo                                                  |

|----------|--------|-------------------------------------------------------------------|

| )        | 41     | ACT/Technico – Solid State Storage Solutions                      |

|          | 33 MCD | Aitech Defense Systems – Where COTS was born                      |

|          | 27 MCD | Alphi Technology Corporation – Modular Solutions for Mil-Std-1553 |

|          | 3      | Annapolis Micro Systems, Inc. – WILDSTAR 5                        |

|          | 24 MCD | Annapolis Micro Systems, Inc. – WILDSTAR 5                        |

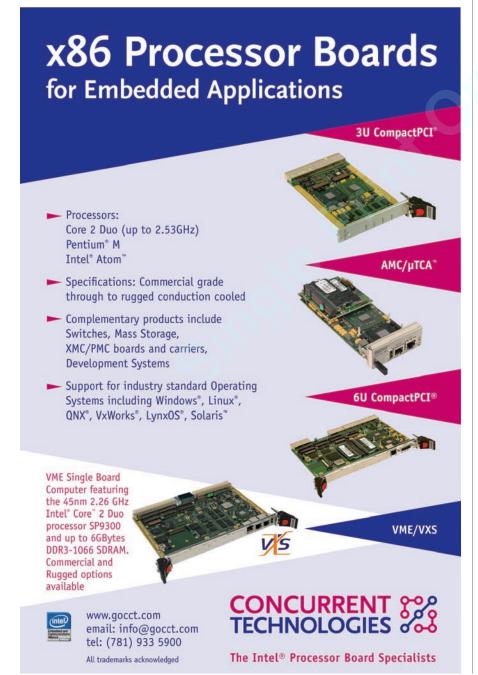

|          | 21     | <b>Concurrent Technologies, Inc.</b> – x86 Processor<br>Boards    |

|          | 36 MCD | Curtiss-Wright – Reduce your development time & costs             |

|          | 35 MCD | Elma Electronic – Cutting-edge backplanes                         |

|          | 25 MCD | Elma Electronic – Cutting it close doesn't cut it                 |

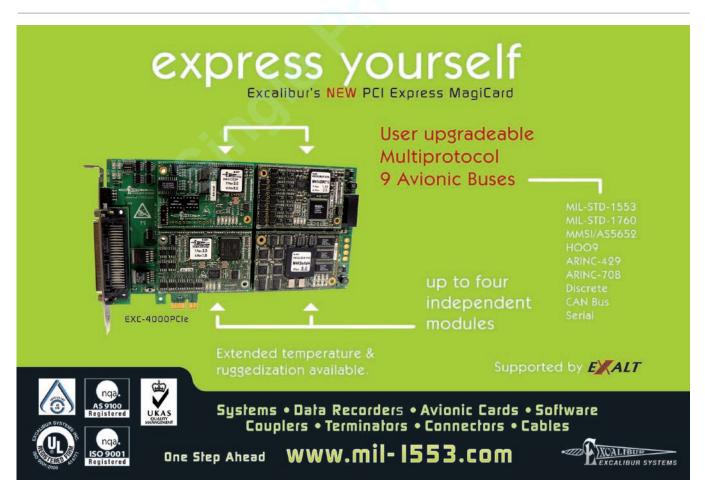

|          | 17     | Excalibur Systems, Inc. – Express yourself                        |

|          | 43     | GE Fanuc Intelligent Platforms, Inc. –                            |

|          |        | Which of these platforms use GE Fanuc hardware?                   |

|          | 6      | Hartmann Elektronik – VME                                         |

|          | 34 MCD | Hartmann Elektronik – VME                                         |

|          |        |                                                                   |

Jacyl Technology Inc. - Python X

|   | Page   | Advertiser/Ad title                           |

|---|--------|-----------------------------------------------|

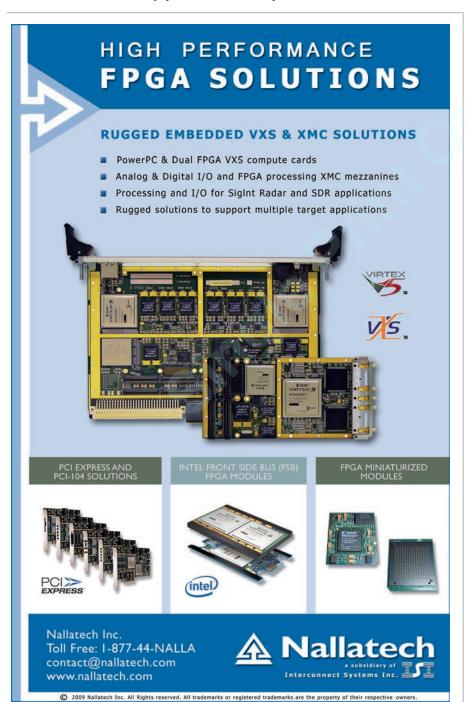

|   | 22     | Nallatech – High performance FPGA solutions   |

|   | 11     | North Atlantic Industries – MIL-STD           |

| S |        | Power Supplies                                |

|   | 10     | Parvus Corporation – Rugged IPv6              |

|   | 2      | Pentek, Inc. – We've Hatched the Next         |

|   |        | Generation of Software                        |

|   | 15     | Phoenix International – Data Storage          |

|   | 28 MCD | Phoenix International – Data Storage          |

|   | 29 MCD | Technobox, Inc. – XMC and PCIe                |

|   | 15     | TEWS Technologies LLC - COTS I/O Solutions    |

|   | 28 MCD | TEWS Technologies LLC – COTS I/O Solutions    |

|   | 38     | Trident Space and Defense – Protect your data |

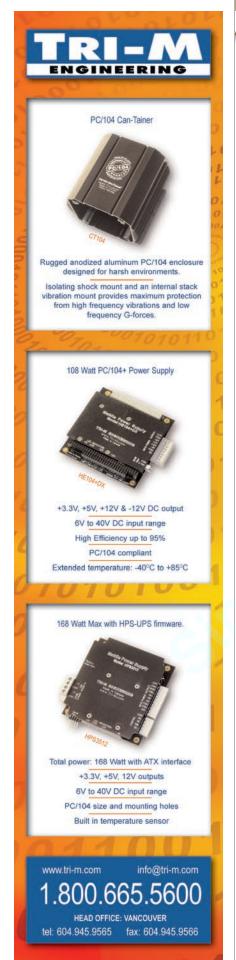

|   | 39     | Tri-M Systems Inc 100Mhz PC/104 Module        |

|   | 20     | Tri-M Systems Inc. – PC/104 Can-Tainer        |

|   | 21     | Twin Oaks Computing, Inc. – CoreDX            |

|   | 16     | VersaLogic Corp Always lands on its feet      |

|   | 8      | White Electronic Designs – We've cleared      |

|   |        | the board.                                    |

# Mil Tech Insider

### **COTS vendors speed FPGA** development cycle

By John Wemekamp

Although FPGAs are now used for DSP in many very diverse applications, they have become indispensable when parallel and repetitive algorithms are required by surveillance, Signals Intelligence (SIGINT), and Electronic Counter Measures (ECM) applications. In military guise, often operating over extended environmental ranges, these applications require the high channel count, I/O bandwidth, high performance, low latency, and small size that only an FPGA-based product can provide. However, the complexity and inherent flexibility of today's devices require prequalified tools, IP components, and a coherent development framework to keep tight project control and achieve realistic time-to-deployment goals. COTS vendors are rising to the challenge of developers' maturing expectations by continuously improving toolsets and product integration.

The case can be so strongly made in favor of using FPGA-based technologies for military sensor processing that the key decision point is now between using internal resources or buying off-the-shelf. Decision makers should weigh factors including time-to-market, the availability of the necessary in-house skills, the cost of training, and the level of risk. Additional consideration should be given to the potential return on investment, which might be measured in size, weight, or power saved, reduced recurring cost, selling in greater quantities, or enhanced competitive differentiation. However, in the defense and aerospace market, production volumes are often small with limited opportunity for direct reuse elsewhere, highlighting the need to keep development cost and risk to a minimum.

### Integration

Because of its many benefits, the FPGA can become the focus of attention when selecting the sensor's overall architecture. It is relatively straightforward to visualize, simulate, and scale the DSP problem to the proposed sensor application using high-level tools such as The MathWorks' Simulink. But equally important is inte-

grating the FPGA with the overall system environment: data acquisition, buffering, internal/external memory control, data path bandwidth, results dissemination, synchronization, error recovery, fault reporting, instrumentation for test and verification, and, finally, proof of operation over the platform's temperature extremes. This mix of internal, external, and interface issues to be resolved will require close integration of tools, libraries, I/O modules, and vendor-supplied IP. When forming part of a heterogeneous processing system, an FPGA must also be integrated with other processor types using common I/O, data structures, and middleware to abstract the detail of differing hardware implementations. Using a switched fabric such as Serial RapidIO is a key element, and vendors are now offering faster, lighter Serial RapidIO IP, prequalified over temperature, targeted to the needs of military DSP architectures.

### System-on-Chip

The capacity, performance, and highly optimized DSP algorithms of the latest FPGA generations make them better able to support an open standards-based SoC infrastructure. Some of these available standards are AMBA, Wishbone, and OpenFPGA. All have the common objectives of offering a comprehensive set of device-agnostic architectural features and facilities to create a framework that supports the development of customers' application IP. Much of the IP support offered by COTS vendors today will be of value in the development of tested and qualified SoC ports for their future hardware products.

### I/O flexibility

Typical off-the-shelf embedded systems, in form factors such as CompactPCI, VMEbus, or newer VPX (VITA 46), offer FPGA-based solutions in a variety of basecard and mezzanine formats. The recently introduced FMC (VITA 57) mezzanine standard adds flexibility by providing a small, optimally sized module for high-speed signal capture with multi-GHz serial signaling to baseboard-mounted

FPGAs. This small form factor makes an FPGA and FMC mezzanine ideal partners for specialized I/O tasks such as protocol or media conversion, legacy communications, and digital video processing.

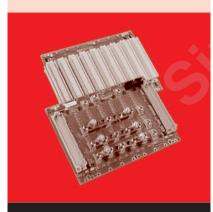

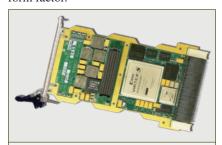

Many military sensors must operate over extreme temperatures. Because of the high power dissipation and GHz+ signaling of a typical large FPGA (10 W to 18 W), thermal design of hardware becomes critical because temperature sensitivity becomes very difficult to identify and diagnose later. Qualified and characterized offthe-shelf modules and tailored IP mitigate these risks and can significantly reduce a project's overall development time. One such qualified module is the FPE320 from Curtiss-Wright Controls Embedded Computing (CWCEC). Shown in Figure 1, it supports both the largest Xilinx Virtex-5 FPGA device types and offers the I/O flexibility of an FMC mezzanine site in the 3U VPX air- or conduction-cooled form factor.

Figure 1 | The FPE320 supports both the largest Xilinx Virtex-5 FPGA device types and offers the I/O flexibility of an FMC mezzanine site in the 3U VPX air- or conduction-cooled form factor.

The promise of significant size, weight, power, and recurring cost reductions continues to stretch developers' resources to achieve their initial development cost and time targets. Considerable gains are possible by using COTS vendor-supplied hardware modules, IP cores, libraries, and drivers. Consequently, this has been proven an effective strategy by many contractors.

To learn more, e-mail John at john.wemekamp@curtisswright.com.

# We've cleared the board.

# It's your move.

Space-saving system-in-a-package and multi-chip solutions from White Electronic Designs free up board space to make room for your big ideas.

Try our new DDR2 SDRAM that packs 1 GByte into a SnPb BGA package less than 1/2 in<sup>2</sup> ... or our new embedded SLC NAND flash BGA that has the performance of a solid state disk drive in a form factor that is one-fourth the volume of a comparable compact flash-based product.

WEDC lean microelectronic solutions are designed to solve component incompatibilities, reduce design complexity, and extend product life and environmental performance in military applications. We offer turnkey design, assembly and test of custom multi-chip solutions and a wide range of standard military off-the-shelf space-saving solutions.

Expand the possibilities; explore your options at www.whiteedc.com/move.

602.437.1520 TEL | 602.437.9120 FAX

It can be a real nightmare when a customer wants a new solution based upon legacy software for which the original developers left no clear indication of design criteria. But finding the proper analysis methodologies and tool suites can help developers get a good night's rest.

Leafing through most sales brochures for software test tools, anyone could be forgiven for thinking that all software projects begin with a blank sheet of paper, a clear set of design criteria, and ample time to design and develop the ideal solution.

In reality, most development work involves the enhancement of existing code, all too frequently developed by a series of application gurus who have left the company and were more keen on getting something working than maintaining documentation or adhering to coding standards.

### Avoiding false dawns

So what kind of nightmare unfolds when an order hinges on such Software of Unproven Pedigree (SOUP) acquiring enhanced functionality? Or worse: What if requirements dictate that modern coding standards need to be retrospectively applied to it (such as JSF++ AV, MISRA-C:2004, the CERT C Secure Coding Standard, or even internal company rules)?

Some software testing products suggest that they can find all your software errors simply by deploying mathematical techniques to predict dynamic behavior through static analysis. It sounds like a dream come true. After all, it saves the developer from rethinking/revamping current programming practices, never mind past ones. However, as in the rest of life, if something sounds too good to be true, it probably is. Such an approach can find some specific runtime errors such as division by zero or out-of-bounds array accesses, and if that is all that is required then it might be a winner. But the false warnings raised are likely to soon lead to sleepless nights in a cold sweat.

Even if it is true that a few runtime errors can be found, the resulting solution has to be proven from a functional perspective, too. No static analysis approach can do that. So, the danger of never finding the errors based on what is required is beyond

doubt a significant nightmare. Customers will not pay, devices are deployed without complete testing, and the specter of what lies behind the unintelligible warnings could haunt the soundest sleeper.

Given that the analysis of dynamic behavior by static means is of limited use, what else is there? What of the better-established dual-pronged approach of sound coding standards coupled with the dynamic analysis of code by execution? Does that really demand a green field application with an idealized development path to become a dream solution?

### Heading out of the darkness

In an effort to change the nightmare into a dream even when the starting code has no complete, written specification, developers need to start with the specification for any amendments and let the original source code simply define the existing behavior. So, the trick is now to capture that existing behavior and ensure that it only changes where change is demanded by the incoming order, even if the new project demands a higher coding standard.

Some dynamic test tools provide just such a point of reference by statically analyzing the source code. The knowledge gleaned is then used to automatically generate unit tests to create a personality profile of the behavior of each existing method or function. Groups of functions can provide a similar role where modularity is not the order of the day. By generating such unit tests on the original code and exercising them on the revised sources, it is possible to ensure that behavior has only changed where change is required.

Although this personality profile approach has merit and makes sleep a little easier, issues remain. For instance, it assumes that the original source code is sound because the application has been proven in the field. But what if some of the new functionality builds on software code that was rarely used there? And even the wellproven parts of the code are likely to now be handling very different data. How will they behave?

Studies indicate that software submitted to only functional testing and field applications is still likely to have code that remains unproven. Dynamic test tools highlight unproven or rarely used execution paths, and static analysis tools help isolate areas that are vulnerable to the newly introduced data sets and in need of more testing. When that work is complete, the personality profile tests

established at the outset are modified to provide a regression test set both to prove the current phase and to ease the path for any additional development work.

In the military world, thanks to enforced DO-178B standards, few nightmare applications are quite this unsettling. However, projects do exist where at least some elements of this extreme scenario ring true. So, it is useful to know which methodologies and which tool suites provide the means to address each of these issues. Prudent, careful use of these proven techniques can yield the results you dream of.

Sleep well.

Mark Pitchford has more than 25 years' experience in software development for engineering applications, the majority of which have involved the extension of existing code bases. He has worked on many significant industrial and commercial projects in development and management, both in the UK and internationally including extended periods in Canada and Australia. For the past seven years, he has specialized in software testing and works throughout Europe and beyond as a field applications engineer with LDRA. He can be reached at Mark.Pitchford@ldra.com.

# Daily Briefing: News Snippets

By Sharon Schnakenburg, Associate Editor

www.mil-embedded.com/dailybriefing

### April's showers produce more than May flowers

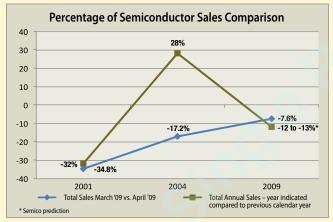

Semico's most recent report on semiconductor sales indicates a case of revenue turnaround - at least when contrasted with ongoing gloomy forecasts. While industry pundits predict a semiconductor sales decline of 20 to 30 percent for 2009, Semico predicts only a 12 to 13 percent 2009 revenue decline in light of "overall market softness." Semico president Jim Feldhan's rationale is derived from what he describes as a quarterly cyclical trend, where the final month of any quarter produces significant sales surges. This, he says, inevitably relegates the following month to a sharp comparative decline. Situated in this tenuous position, April has historically seen this decline range between 17.2 percent (in 2004) and 34.8 percent (in 2001) in comparison with March sales. The silver lining for April 2009 materialized in the form of a "record" low sales decline: only 7.6 percent in comparison with March 2009. Meanwhile, industry strongholds for 2009 are forecasted to include GPS systems, netbooks, and HDTV, among others.

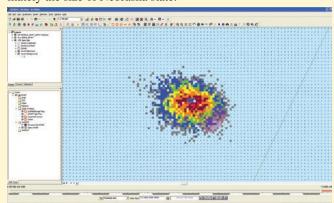

Figure 1 | Semico predicts only a 12 to 13 percent 2009 revenue decline in light of "overall market softness."

### RoboScout to enlist in the **German military**

The more lives that can be spared on the battlefield by using unmanned technology, the better, as implied by the German Military of Defense's new RoboScout project. Presently in the development stage, prime Base Ten Systems Electronics GmbH (Base 10) will incubate the modular Unmanned Ground-based Vehicle (UGV), earmarked to handle multiple roles including reconnaissance, SIGINT, support of satellite and terrestrial/radio data links, and aiding other vehicles' communications by serving as a relay station. To facilitate said communications transmissions while proffering deterministic messaging, high reliability, and real-time low-latency performance, Real-Time Innovations (RTI) will provide its Data Distribution Service middleware. The middleware features a publish-subscribe model and is predicted to ease RoboScout's future expansions and upgrades.

### Military technology meets the "Terminator"

Some philosophers theorize that life imitates art, but does art imitate – or utilize – technology? Yes, in the case of the recently released "Terminator Salvation" movie, where a triad of Crystal Group Inc.'s real-life military technology wares appear in the movie's command center workstation: the rugged RS47F and RS234T servers, along with the RD2217 rugged display. Crystal Group's immortalized military offerings are tough enough to take on the same extreme environmental threats depicted in celluloid, according to the company, presumably even Skynet's nuclear annihilation. Proving the point is the RD2217, a rugged dual 17" 2U EIA display, which meets MIL-STD-810F's operational temp (0 to +55 °C), storage temp (-55 °C to +85 °C), altitude (12,500 ft operation; 40,000 ft transport), and vibration (5 GRMS, 5-500 Hz, 75 min/axis) requirements (with vibration kit).

### **Coast Guard software** hastens search

When Air France Flight 447 recently fell into the Atlantic Ocean, French authorities knew they needed to recover passengers and crew, flight wreckage, and the aircraft's data recorders as quickly as possible. Assisting in the sobering endeavors was the U.S. Coast Guard, whose efforts were hastened with its Search and Rescue Optimal Planning System (SAROPS) software system. SAROPS predicts a search area by analyzing floating wreckage locations in conjunction with wind, weather, and sea conditions during a specified time period to estimate a plane's likely location. SAROPS – developed collaboratively by Northrop Grumman, Applied Science Associates (ASA), and Metron, Inc. – additionally accesses data from radar, satellites, models, and in-situ observations to allow SAR controllers to rapidly examine probable scenarios. As of press time, Flight 447's precise crash locale is not yet determined and its data recorders are still missing, perhaps laying somewhere within the identified 77,220 square mile (200,000 square km) search area: approximately the size of Nebraska state.

Figure 2 | SAROPS search and rescue technology, figure courtesy of Applied Science Associates (ASA).

### Pilots preview their future before it happens - with 100% availability

Many people would love to live in or view their own future before it happens - and without the possibility of any lasting consequences. Though time travel isn't a reality just yet, the F-15E Mission Training Center located in Suffolk, England might be the next best thing. A joint project of prime The Boeing Company and the U.S. Air Force, the center - in operation since April 2008 - recently ascended to the "100 percent availability" milestone. Giving military pilots in training the chance to fight before they actually face the real world, the center contains a duo of high-fi, dual-cockpit F-15E simulators. Each simulator is equipped with a cutting-edge visual system providing realistic 360-degree visuals within a synthetic environment. The simulators' 3-D imagery, rendered by Quantum3D Inc.'s Independence image generator, flies by at 60 Hz. To date, the center has supported 400-plus training missions.

Figure 3 | The F-15E Mission Training Center located in Suffolk, England recently reached "100 percent availability" (photo courtesy of Boeing)

### Radar breaks new ground ... kind of

Though a recent contract between a U.S. Army agency and Curtiss-Wright Controls Embedded Computing's (CWCEC's) 3d-Radar group has been described by company officials as "groundbreaking," ironically CWCEC's summoned Ground Penetrating Radar (GPR) technology works in advance of breaking any ground. Under the agreement, CWCEC will provide its GeoScope and B3231 antenna technologies for the primary purpose of detecting Unexploded Ordnances (UXOs) and other buried objects. The Army's version contains enhancements including the GeoScope's "real-time view," which provides operators the capability to see post-processed GPR data – within mere milliseconds of data's initial acquisition. Detection algorithms from Exponent, Inc. were integrated with the real-time view, and deliveries to the U.S. Army are expected through March 2010.

### AMD's Radeon: In less-familiar territory

A prevalent contender in PC markets, AMD is now soaring into the embedded safety-critical avionics industry with its ATI Radeon E4690 GPU - empowered by ALT Software's DO-178B-certifiable 2D/3D OpenGL drivers. The ATI Radeon E4690 renders in excess of 3x the ATI Radeon E2400 embedded graphics accelerator's performance. The ATI Radeon E4690 also provides a PCI-E 2.0 x16 interface, along with 512 MB on-chip memory and a 128-bit memory interface. Meanwhile, ALT Software, Wolf Industrial Systems, and Channel One recently announced their Advanced Graphics Solutions (AGS) Group, which aims to develop end-to-end technology tailored around the ATI Radeon E4690 graphics accelerator.

### **Platform readies C4ISR technologies**

Ensuring warfighter success is contingent upon effectively developing, testing, and fielding deployable wares to the battlefield. One proof of concept is Lockheed Martin's Airborne Multi-INT Laboratory (AML), which renders a platform for researching, testing, and demonstrating new C4ISR capabilities, to prepare for future deployment (Figure 4). AML will aid in investigation of emerging Reconnaissance, Surveillance, and Target Acquisition (RSTA) methods, in addition to facilitating the development of an operational concept touted to link all echelons' battlefield resources. Anticipated experimentation exercises consist of improving end-to-end intelligence, beginning with the initial concept and proceeding to sensor cross-queing, exact geolocation, and finally, fast transmission to end users. Additionally, AML's Service Oriented Architecture (SOA)-based architecture enables reach-back to other databases and information sources and accommodates cyber security schema integration.

Figure 4 | AML photo courtesy of Lockheed Martin

### Satellite to provide insight for smartphone-size devices

Space Systems/Loral's (SS/L's) well-traveled TerreStar-1 satellite has come a long way – and is still on the move (Figure 5). First, it was launched from the European Spaceport in French Guiana onboard an Ariane 5 rocket. Next, its first thruster firing transpired in early July, with the goal of propelling TerreStar-1 to its final geostationary orbital locale at 111.0 degrees West longitude. The final goal: The satellite's 18-meter antenna reflector,

designed for umbrellalike unfolding once it gets to its orbital slot, will facilitate video, data, and voice transmissions to smartphonesized mobile devices utilizing a 2 GHz spectrum. The progeny of SS/L's joint effort with Hughes Network Systems, TerreStar-1 includes a Ground-Based Beam Forming (GBBF) system that can direct the satellite's power where it's most needed at any given time. TerreStar-1 can generate spot beams over the continental U.S., its territories, and Canada.

Figure 5 | TerreStar-1 photo courtesy of Space Systems/Loral

The challenge was to implement high-performance Synthetic Aperture Radar (SAR) for two platforms in one week.

The need for high-performance Signal- and Image-Processing (SIP) applications is driving interest in parallel and multicore hardware for military embedded systems. However, programming such complex architectures can increase development costs by reducing developer productivity and code reuse. Leveraging a library that implements the high-level VSIPL++ API provides a way for SIP software developers to take advantage of the performance potential of parallel and multicore hardware systems while satisfying schedule and cost constraints.

### The problem: Getting from prototype to high-performance production code efficiently

Consider the following challenge. A software developer has a Scalable Synthetic Aperture Radar (SSAR) benchmark expressed in 50 lines of MATLAB code. The developer needs to implement that benchmark to achieve good performance on two very different systems – a conventional x86 processor and a heterogeneous, multicore Cell Broadband Engine (Cell/B.E.) processor – in just one week.

For background, Synthetic Aperture Radar (SAR) is used for a variety of imaging and remote sensing applications, including reconnaissance, surveillance, and terrain mapping. To standardize benchmarking this common algorithm, MIT Lincoln Laboratory created a scalable synthetic SAR application as part of the High Performance Embedded Computing (HPEC) Challenge[1]. The benchmark demonstrates the intense computational requirements found in actual systems using synthetic (and scalable) data. The raw radar returns are processed by means of a 2D Fourier matched filtering step, a spatial frequency interpolation step, and a transformation back to the spatial domain. Key mathematical operations, as in any SAR application, include FFTs, matrix multiplication, and interpolation. Thus, a software development technique that offers benefits for this SSAR's benchmark points to an approach that is likely to work for larger SIP applications as well.

### The first step: Choosing a library-based solution

If high performance were the only goal, the developer could consider coding the algorithm in a low-level language such as C or assembly code. But the time constraints (only a week), combined with the need to develop for both an x86 and a Cell/B.E. processor, make this approach unworkable.

With a portable library, though, the same application code will run on more than one system. And a library allows a developer to program for an unfamiliar architecture, such as the Cell/B.E., in a familiar language using familiar development tools. The key is to find a library at the right level of abstraction – high enough to provide the necessary primitives for the application domain but low enough to allow for efficient implementations and thus high performance.

For the SSAR benchmark, the VSIPL++ API provides the right level of abstraction. VSIPL++ is an open standard[2], high-level API for parallel high-performance signal and image processing. It is defined by the High Performance Embedded Computing Software Initiative (HPEC-SI – www.hpec-si.org), a consortium of industrial, academic, and governmental partners, with sponsorship from the Air Force Research Laboratory. Its goal is to simultaneously deliver productivity, portability, and performance. VSIPL++ defines a pure C++ interface for operations – including FFTs, filters, linear system solvers, and other mathematical functions – that allow SIP applications to be written at the problem domain level.

For the SSAR benchmark challenge, CodeSourcery used Sourcery VSIPL++, a library that provides an optimized implementation of the VSIPL++ API on x86, Power Architecture, and Cell/B.E. processors with useful extensions to the base VSIPL++ specification.

### The next step: Implementing SSAR in VSIPL++

Using the VSIPL++ library, CodeSourcery implemented SSAR in C++ in just four days. To illustrate the relative advantage of the VSIPL++ API for developer productivity, Figure 1 shows three different implementations of the SSAR algorithm's fast time filter: (1) MATLAB, (2) simple, unoptimized C[3], and (3) VSIPL++. Mathematically, they all perform the same computation, but the VSIPL++ version, like the MATLAB version, is easy to understand because it is expressed in SIP primitives such as FFTs and matrix multiplication.

### **MATLAB** # Filter echoed signal along fast-time sFilt = fft( sRaw ) .\* ( fastTimeFilter \* ones(1,mc) ); # Compress signal along slow-time sCompr = sFilt.\* exp(ic\*2\*(ks(:)\*ones(1,mc)) ... .\* $(ones(n,1)*sqrt(Xc^2+(-ucs).^2)) - ic^2*ks(:)*Xc*ones(1,mc));$ ftx2d(S,Mc,N); for(i=0;i<N;i++) { $for(j=0;j<Mc;j++){}$ tmp\_real=S[i][j].real; tmp\_image=S[i][j].image; S[i][j].real=tmp\_real\* Fast\_time\_filter[i].real-tmp\_image\*Fast\_time\_filter[i].image; S[i][j].image=tmp\_image\* Fast\_time\_filter[i].real+tmp\_real\*Fast\_time\_filter[i].image; for(i=0;i<N;i++) { for(j=0;j<Mc;j++)tmp\_value=2\*(state->K[i]\*(sqrt(pow(Xc,2)+pow(Uc[j],2))-Xc)); cos\_value=cos(tmp\_value); sin\_value=sin(tmp\_value); fp[i][j].real=S[i][j].real\*cos\_value-S[i][j].image\*sin\_value; fp[i][j].image=S[i][j].image\*cos\_value+S[i][j].real\*sin\_value; VSIPL++ Setup Matrix<complex\_t> s\_compr\_filt(...); s\_compr\_filt = vmmul<col>(fast\_time\_filter, exp(complex\_t(0, 2) \* vmmul<col>(ks, nmc\_ones) \* (sqrt(sq(Xc) + sq(vmmul<row>(ucs, nmc\_ones))) - Xc))); col fftm type ft fftm(Domain<2>(n, mc), 1); **VSIPL++ Compute** // Filter echoed signal along fast time and compress s filt = ft fftm(s raw) \* s compr filt;

Figure 1 | The VSIPL++ implementation of the SSAR fast time filter, like MATLAB, is much more compact than the unoptimized C.

Ignoring the setup of the filter coefficients, the VSIPL++ version of the fast time filter requires a single line, performing two dataparallel operations sequentially. By contrast, the C reference implementation is more verbose and thus more error prone. In addition, because the C code is iterative, it is more difficult to divide among multiple processors or to optimize for different architectures.

The C and VSIPL++ implementations were benchmarked on both a conventional Xeon processor running at 3.6 GHz and a Cell/B.E. processor running at 3.2 GHz. The entire front-end processing chain was run looping over the data 10 times to average out the measurements. On the Xeon platform, the VSIPL++ library used the Intel Performance Primitives (IPP) library v5 and Intel Math Kernel Library (MKL) v7.21 as well as FFTW v3.1.2. On the Cell/B.E. platform, the VSIPL++ library used the Cell Math Library v1.0 and FFTW v3.2-alpha3. The VSIPL++ code needed no changes to run on both architectures; the VSIPL++ library utilized these underlying math libraries without explicit direction from the developer.

Because development costs vary roughly linearly with the number of lines of code, it is important to look at performance and Source Lines Of Code (SLOC) count together to understand the relationship between developer effort and performance benefit. Here, the VSIPL++ version offers both productivity and performance

improvements over the C reference implementation on two very different processors. The VSIPL++ version requires 48 percent fewer lines of code and achieves speedups of 68x and 146x on the Xeon and Cell/B.E. platforms, respectively. Tables 1a and 1b show the source line counts and performance of the VSIPL++ and C implementations of the core 2D Fourier matched filtering and interpolation routines.

The VSIPL++ approach offers particular advantages on the Cell/B.E. processor because it relies on the VSIPL++ library's implementation of the SIP primitives. Several of the primitives

| Table 1a: SLOC    | MATLAB | Unoptimized C | VSIPL++ |  |

|-------------------|--------|---------------|---------|--|

| Matched Filtering | 24     | 109           | 17      |  |

| Interpolation     | 22     | 76            | 23      |  |

| Setup/Other       | 4      | 206           | 163     |  |

| Overall Total     | 50     | 391           | 203     |  |

used in the SSAR algorithm, such as two-dimensional FFTs and the matrix multiplication operations used for filtering in the frequency domain, are computationally intensive and also involve significant data movement to and from the eight Synergistic Processing Elements (SPEs) of the Cell/B.E. processor. Getting good performance from the SPEs requires carefully balancing the input and output of data with the computations being performed. Optimizing a C implementation to achieve comparable performance would greatly increase program complexity and thus would drive up development time and cost.

### The extra mile: Unlocking hardware's potential with strategic optimization

Finally, opportunities for optimization were investigated in the VSIPL++ implementation for the Xeon and Cell/B.E. processors. For example, in the fast time filter computation (see again Figure 1), the VSIPL++ code performs an FFT followed by a matrix multiplication. Given large enough data sets, memory accesses in the second step cause cache misses on a Xeon processor,

| Table 1b:                                                                                                                                 | Unoptimized C |           | VSIPL++   |           | Optimized VSIPL++ |           |

|-------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------|-----------|-----------|-------------------|-----------|

| Performance                                                                                                                               | Xeon          | Cell/B.E. | Xeon      | Cell/B.E. | Xeon              | Cell/B.E. |

| Matched Filtering                                                                                                                         | 13.6 MF/s     | 4.5 MF/s  | 1.57 GF/s | 29.6 GF/s | 3.17 GF/s         | 30.6 GF/s |

| Interpolation                                                                                                                             | 23.2 MF/s     | 7.9 MF/s  | 1.12 GF/s | 0.4 GF/s  | 1.13 GF/s         | 5.6 GF/s  |

| Overall Total                                                                                                                             | 16.9 MF/s     | 5.6 MF/s  | 1.15 GF/s | 0.8 GF/s  | 1.71 GF/s         | 9.9 GF/s  |

| Tables 1a and b   SLOC vs. performance: VSIPL++ requires 48 percent fewer lines of code than C and yet runs 68 times faster even on Xeon. |               |           |           |           |                   |           |

# Always lands on its feet

VersaLogic's Manx Single Board Computer (SBC) offers a high degree of functionality at an affordable price. With a 500 MHz AMD® Geode LX 800 processor, this tough SBC makes good on its promise of mid-level performance in a low power, compact footprint. The hard working Manx offers 256 MB of rugged soldered-on RAM and is available in standard (0° to +60°C) and extended (-40° to +85°C) temperature versions. Manx features extensive integrated I/O, 10/100 Ethernet, high performance video

capabilities, and supports removable, bootable flash memory in an optional latching socket. Customization is available on quantities of 100 pieces or more.

With more than 30 years experience delivering extraordinary support and on-time delivery, VersaLogic has perfected the fine art of service: One customer at a time. Contact us today to experience it for yourself.

1.800.824.3163 1.541.485.8575 www.VersaLogic.com/mnx

leading to expensive reads from main memory. Rewriting this loop so that each row is processed one at a time (that is, taking the FFT and then performing the vector multiplication) results in a 1.6x speed improvement for this portion of the code. The change is trivial to implement, requiring only a net increase of eight lines of code, yet it yields a 20 percent improvement in the execution time of the entire front-end stage.

On the Cell/B.E. processor, profiling reveals that interpolation takes almost 40 times longer than matched filtering. A large amount of time is spent in a loop over data in the "range" direction (perpendicular to the flight path), performing a polarto-rectangular coordinate conversion. A contribution from several inputs for each side-lobe of the sinc function used in the interpolation is added to calculate the intensity and phase of the corresponding output pixel. This computation cannot be expressed well using VSIPL++ primitives.

To improve performance, CodeSourcery used a VSIPL++ API extension available in Sourcery VSIPL++ called "user-defined kernels." User-defined kernels allow the developer to write a high-performance computational kernel and still leverage the data-handling aspects of the VSIPL++ library. A hand-coded kernel with 208 lines of code speeds up interpolation from 4.23 seconds to 0.18 seconds, an improvement of more than 23 times that of the original implementation.

On Xeon, the final optimized code runs more than 82 times faster than the C reference implementation. On the Cell/B.E., it was 5.7 times faster than on the Xeon and more than 1,400 times faster than the reference C code. Even modest, easy-to-implement changes can significantly improve performance.

### Combining performance, productivity, and portability with VSIPL++

Using a library implementing the open-standard VSIPL++ API made possible the development of a complex application in far fewer lines of code than are necessary in C. Out of the box, this code outperformed the C reference implementation. With limited changes to address performance bottlenecks, performance was further enhanced. And the application remained portable across vastly different architectures.

#### **References:**

- 1. Haney R., et. al. The HPEC Challenge Benchmark Suite. Proceedings of the Ninth Annual High-Performance Embedded Computing Workshop (HPEC 2005), Lexington, MA, September 2005.

- 2. VSIPL++ Specification 1.0. Georgia Tech Res. Corp. 2005, (or online at www.hpec-si.org).

- 3. SSCA #3 SAR sensor processing, knowledge formation, and file I/O. High Productivity Computer Systems (HPCS) website, www.highproductivity.org/ SSCABmks.htm, 2007 (Meuse, T.: MATLAB implementation source code, Meng-Ju and McMahon, J.: C implementation source code).

**Don McCov** is a software developer in CodeSourcery's High Performance Computing group. He has worked for CodeSourcery since 2005 as a member of the Sourcery VSIPL++ development team. Prior to joining CodeSourcery, Don had more than 10 years of experience developing embedded software applications related to high-speed data pro-

cessing. He holds a B.S. in Applied Physics from the University of Delaware. He can be reached at don@codesourcery.com.

> CodeSourcery 888-776-0262 www.codesourcery.com

### Hardware: Net-centric operations

### **General Dynamics** and WIN-T: Pursuing the GIG

Figure 1 | Increment 2's development testing, paired with Increment 3's technologies maturity evaluation, was held September through December 2008 at Fort Huachuca, Arizona. (photo courtesy of General Dynamics)

### By Sharon Schnakenburg, Associate Editor

Much like the constantly on-the-move soldiers it aims to inform and protect, the Global Information Grid (GIG) and its technological components never seem to stand still. One example is the U.S. Army's GIG-enabling Warfighter Information Network-Tactical (WIN-T) communications/networking program, with its always-moving, ever-evolving technologies.

WIN-T forms the network infrastructure of the U.S. Army's section of the GIG. "It's the equivalent of what you would have in, say, your data closet in an office building," explains Bill Weiss, vice president tactical networks for General Dynamics C4 Systems. WIN-T networking gear can be embedded into combat vehicles and installed in tactical communication assemblages, and provides broadband Internet, information services, and telephone services to command posts from theater through company levels.

Meanwhile, WIN-T's ever-evolving "increments" (see Sidebar 1), hardware and software components, and ties to the Army's new FCS transition depot – the Brigade Combat Team (BCT) Modernization Strategy – are what make it intriguing.

### A B C and D of WIN-T increments

Increment 1: Also referred to as the Joint Network Node; provides network services to command posts at the halt; now deployed to more than half the U.S. Army.

Increment 2: Provides a mobile networking capability "so a commander has access to information ... even if he's in his vehicle moving along at 60 mph," details Bill Weiss, vice president tactical networks for General Dynamics C4 Systems. Ultimately will include more than 2,000 nodes and service 10 divisions and 40 brigade combat teams1. Development testing occurred September through December 2008 at Fort Huachuca, Arizona (Figure 1). Limited user tests were completed in March 2009.

Increment 3: Delivers mobile networking capability with improvements on Increment 2, including airborne relay capability and upgraded satellite and line-of-sight radio communications in a smaller package; limited user testing anticipated in 2011.

Increment 4: A long-term upgrade program to integrate bandwidth from the TSAT program, and more. (TSAT is on SECDEF Robert Gates' proposed budget's cutting board, however.)

Sidebar 1 | WIN-T's fourfold increments

### Hardware and software composites

Weiss says Increment 2 features specialized network radios optimized for mobile use with their logical counterparts – omnidirectional beamforming antennas – to facilitate line-of-sight communications established on an ad hoc, as-needed basis. A built-in navigation system and satellite pointing mechanism are key.

Networking gear additionally consists of oft-ruggedized, off-theshelf switches and routers. Prime contractor General Dynamics - whose WIN-T team members include Lockheed Martin and Program Executive Office Command, Control, and Communications Tactical, among others – sometimes partners with commercial vendors Cisco and Juniper Networks to create smaller routers when space is limited. (See Table 1 for a list of additional WIN-T suppliers.)

Meanwhile, WIN-T's software blends off-the-shelf and custom programs. Commercial software is used for network services, commercial routing, and commercial network management. Proprietary software is created for the specialized waveforms and automation necessary for supporting the mobile network.

### Ties into FCS and BCT modernization strategy

WIN-T Increment 3 is the first WIN-T increment associated with FCS – which is now transitioning into what the Army calls its Brigade Combat Team Modernization Strategy - utilizing JC4ISR embedded radios and designed to meet FCS vehicle SWaP requirements. Though SECDEF Gates has put all except the initial FCS increment on the proposed chopping block, General Dynamics continues with its various WIN-T increments - undaunted.

### **WIN-T** embedded systems suppliers and wares

Wavestream's solid-state amps

Cisco's Unified Communications Manager Software

General Dynamics' GoBook XR-1 computer

TRAK Microwave Corporation's Modular Time Code Processor

Network Equipment Technologies, Inc.'s NX1000 multiservice networking platform

**Expand Networks' Accelerator Operating System**

Netcordia's NetMRI network change and configuration management tool

Table 1 | These are just some of the companies providing their wares to one or more WIN-T increments.

<sup>&</sup>lt;sup>1</sup> The government classifies one mobile node of WIN-T Increment 2 possessing a TCN, POP, and SNE.

Faced with growing network usage, the DoD can look to deep packet inspection to differentiate authorized, unauthorized, and recreational traffic at a deeper level for better security, bandwidth management, and overall information assurance.

Modern warfare places very particular requirements on network communications infrastructure. As the Department of Defense (DoD) evolves to support a netcentric environment, the agency's networks are critical to maintaining the secure collaboration and information sharing necessary for a common operational picture of the battlefield and mission operations.

Yet DoD networks also support a wide range of traffic that is not mission critical. With a growing pool of next-generation converged applications, like VoIP and streaming multimedia, unauthorized and recreational use of the network increasingly occupies the bandwidth needed for vital mission operations. In addition to placing a heavy strain on defense networks, this high volume of unauthorized network traffic conceals malicious content from security tools.

The inherent threat posed by a larger user population along with a greater appetite for mission-critical information means that the DoD needs to fully understand and manage who is on the network, what users are doing, and the resources to which they have access. DoD network administrators must look beyond legacy network analysis methods toward the implementation of Deep Packet Inspection (DPI) technologies to keep the agency's networks reliable, timely, and secure.

### DoD threats, both foreign and domestic

According to informal estimates, 70 percent of DoD network traffic is deemed

"unofficial." This means that traffic unrelated to DoD business is largely dominating the agency's available bandwidth, diminishing the throughput available to conduct and support missions, and harming network security.

For example, streaming media websites like YouTube are particularly troublesome for DoD networks. Often quite large, these files can create asymmetric traffic flows that lead to bandwidth problems. Independent analysis of DoD network traffic finds that use of such streaming media websites peaks during high-profile events such as the NCAA March Madness tournament and the Olympics.

Needless to say, this recreational use of bandwidth poses a very real threat to national security. In fact, a recent DoD report to the Senate Armed Services Committee on DoD personnel access to the Internet highlighted that, if left unchecked, unauthorized and recreational use of DoD networks can leave less bandwidth available for, and even obstruct, mission-critical data transfers. In addition, and frankly even more problematic, by creating an even higher volume of traffic, recreational use potentially camouflages and allows intruders, viruses, and other malicious threats to masquerade as benign traffic. According to a report to Congress on DoD Personnel Access to the Internet[1], Peer-to-Peer (P2P) traffic, like music file sharing from Kazaa, can be especially dangerous since it often introduces corrupt files to the network and can elude traditional security tools.

Recent observations of the DoD's inbound network traffic indicate that the overwhelming majority is associated with ports typically related to Web traffic, which are outlined in Table 1. By itself, this association does not imply that the traffic is legitimate.

| Common TCP/IP Port Numbers |                                   |  |  |  |

|----------------------------|-----------------------------------|--|--|--|

| Port Number                | Application                       |  |  |  |

| Port 21                    | FTP File Transfer                 |  |  |  |

| Port 25                    | SMTP E-mail Delivery              |  |  |  |

| Port 80                    | HTTP - Internet Traffic           |  |  |  |

| Port 110                   | POP3 Mail Delivery and Collection |  |  |  |

| Port 143                   | Remote E-mail Access (IMAP4)      |  |  |  |

Table 1 | The majority of traffic inbound to the DoD is associated with these typical Web ports, but this association does not imply that the traffic is legitimate.

In fact, oftentimes this traffic represents malicious activity that simply "disguises" itself as legitimate Web traffic. Cyberrelated attacks on agency networks increased 158 percent in 2007, according to the Department of Homeland Security (DHS), and disguised traffic is likely in part responsible for this sharp uptick. Considering this very real and growing threat, the DoD must eliminate the potential for recreational network use to contribute to potential security lapses.

As an example of efforts underway to tackle the network security and bandwidth challenge, the Defense Information Systems Agency (DISA) put in place

the Global Information Grid - Bandwidth Expansion (GIG-BE) program to increase bandwidth and diversify physical access to approximately 87 critical sites in the continental United States. The DoD also blocks access to popular recreational websites such as YouTube, MySpace, and Photobucket on official military computers in the battlefield.

While these proactive efforts help improve network reliability, some of the methods are limited, at best, in their capabilities. What is needed are DPI-enabled applications that offer richer visibility into the traffic traversing the network.

### DPI: A policy-centric approach to a net-centric challenge

To protect the integrity of DoD networks and ensure sufficient bandwidth for essential operations, administrators must determine the exact nature of the traffic consuming network bandwidth, as well as block or prioritize traffic with networkwide policy enforcement. What's more, detection and analysis must take place without compromising network speed or adding latency.

Through standard Transmission Control Protocol (TCP)/Internet Protocol (IP) networking, data is sent between systems using small packets that quickly traverse the network and are reassembled at the respective end points to recreate the original information. The purpose of current traffic monitoring and management technologies is to scan the individual data packets to detect specific patterns, issue alerts about attacks or unauthorized use, and block harmful activity.

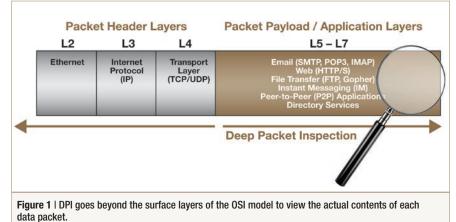

For instance, common security applications include Intrusion Detection Systems (IDS), Intrusion Prevention Systems (IPS), and firewalls. Firewalls are generally used to block harmful traffic at Internet ports or suspect IP addresses. Many modernday firewalls can also identify and block harmful protocols. While firewalls inspect both inbound and outbound traffic, they only provide protection at the deployment site, do not protect the network at the fourth through seventh levels of the Open Systems Interconnection (OSI) model, and also do not articulate policies to determine rights of access. Figure 1 illustrates the additional visibility offered by DPI-enabled technologies.

DPI-enabled devices, on the other hand, permit the transfer of extremely large amounts of data at wire speed while giving unprecedented visibility into deeper levels of network traffic to identify and remedy security vulnerabilities and unauthorized use.

Operating at layers two through seven of the OSI model, DPI-enabled applications can direct, filter, and log IP-based applications and Web traffic, regardless of the protocol or application type, by searching for defined protocol-specific characteristics such as URLs for http or an e-mail address for SMTP in the data's "DNA." These variables are configured by the network administrator in a rules or policy engine that implements those polices according to signaturebased comparisons; heuristic, statistical, or anomaly-based techniques; or some combination of these. For example, many DPI devices can identify packet flows (in addition to conducting a packetby-packet analysis), allowing the implementation of control actions based on accumulated flow information.

By nature, DPI applications require definitions of each applicable protocol in

order to operate. Thousands of Ethernet protocols exist, each with their own unique session format. Moreover, these protocol definitions change frequently due to modifications from standards groups or the introduction of new protocols. While many L4 security devices only examine the IP header of a data packet to identify the IP and port information before making packet-handling decisions, DPI systems can solve greater packet processing challenges due to a more comprehensive examination of data protocol and characteristics.

Purpose-built DPI platforms can combine the functionality of an IDS, IPS, and firewall as well as any other DPI-based applications (that is, those for lawful intercept and data leakage prevention), thus delivering significant additional features and protections to allow network administrators to streamline and secure traffic flow. A message tagged as "high priority," such as a mission-critical communication, can be routed to its destination ahead of low-priority messages or packets involved in recreational activities such as viewing sports highlights or listening to streaming radio. The deeper level of visibility also means that malicious data associated with unauthorized use can be identified and acted upon. This capability is essential to combating the challenges presented by recreational or unauthorized use of military networks.

### **Big Performance** in a Small Package

Need a flexible, openarchitecture communications infrastructure?

Concerned about data interoperability?

Struggling with constrained resources?

Save time and money by using a proven, interoperable communications middleware solution.

CoreDX provides a robust, quality-of-service enabled Data Distribution Service. Our implementation is perfect for embedded systems with constrained resources and a need for high-throughput, low-latency communications.

Integrate CoreDX today and launch your product.

### A common operational platform for network management

DPI-enabled appliances enhance the capabilities of traditional security, traffic management, and network monitoring and analysis solutions. Ideally, the DoD should look to deploy these technologies on one common operational platform leveraging both internally developed Government Off-the-Shelf (GOTS) applications and Commercial Off-the-Shelf (COTS) applications. The network devices must keep pace with

multi-gigabit line rates and support realtime deep-packet processing.

To satisfy the requirements for DPI, a platform must be:

- Linux-based, as a majority of forward-leaning security and network monitoring applications are open source and Linux-based

- Customizable to accommodate ever-changing network solutions requirements

- Cost-efficient, since physical space, facilities, and power costs force the DoD to make budget-conscious, high-performance decisions

- Programmable so the DoD can rapidly develop, deploy, and manage mission-critical operations, new services, and applications

- Policy-centric, allowing the DoD to define its own policies for network traffic

- IPv6 supported, since the government has mandated the adoption of Internet Protocol version 6 (IPv6) this year

Meeting the DoD's vision of a secure and robust network supporting all information classification levels and collaboration requires unique network analysis and control capabilities. Supported by a flexible platform and comprehensive policies, DPI-enabled applications surpass traditional security tools to provide an unprecedented level of visibility for sound bandwidth and security controls. Ultimately, this technology can help the DoD find the right balance between encouraging communications and innovation while also protecting the security and integrity of DoD data.

### References:

1. Report to Congress: A Report in Response to Request on Page 323 of Senate Armed Services Committee Report Number 110-77: Department of Defense Personnel Access to the Internet, Sept. 2007, www.dod.mil/ pubs/foi/other/SASC\_response\_ report110-77\_0907.pdf

Kevin Curran is Vice President of Federal Sales at Bivio Networks. A 20-year IT industry veteran, he holds a Bachelor's in **Business Adminis-**

tration and Finance from Virginia Tech and is an active member of the Armed Forces Communications and Electronics Association (AFCEA) and the American Council for Technology/Industry Advisory Council (ACT/IAC). He may be reached at kcurran@bivio.net.

> **Bivio Networks** 925-924-8600 www.bivio.net

# MIL/COTS The Defense Electronic Product Source DIGEST

July/August 2009

### In This Issue

### The changing face of SBCs

For years, the largest number of new embedded products crossing our desks were SBCs on 6U-sized LRUs. That stands to reason, since

nearly every system needs one of them usually stuck in a VME backplane's Slot 1. But the advent of processors bolted to mezzanine cards such as PMC or XMC, in addition to the new VITA 59 System-on-Module (SoM) specification, has fragmented the market a bit. We're now receiving new processor type products that don't resemble the traditional 6U SBC of yore. And even more interestingly, we're seeing more sensor mezzanine cards where the CPU of choice - essentially also making them "SBCs" by definition – is not a processor at all. Instead, most mezzanines now include an FPGA engine into which hard- or soft-core CPUs are embedded.

Herein you'll find 19 new-to-us, hand-selected VME-related products in this "All About VME" MIL/COTS DIGEST supplement. Not all form factors are strictly VME, though. You'll find: 2 "traditional" VME SBCs, both equipped with Core 2 Duo Intel CPUs, along with 1 PowerPC-based VPX SBC and a VITA 59 SoM also with a Core 2 Duo. There are 2 Ethernet boards or switches, in VPX and optional CompactPCI versions. Depending upon how you slice it, there are 3 to 5 PMC, XMC, and FMC (FPGA mezzanine card) modules here - most of which include high-res A/D front ends supplemented by Altera Stratix II or Xilinx Virtex-5 FPGAs. Finally, we've included a handful of chassis (including one that's mist cooled) and a backplane ready to accept VME64, VPX, or CompactPCI boards. All in all, this MIL/COTS DIGEST provides a great cross-section of the evolving VME ecosystem.

Mis A. Cinf

Chris A. Ciufo, Editor

# **3U VPX Ethernet** switch

he VPX6-683 FireBlade switch provides a fast, secure approach to interconnect subsystems, chassis, cards, and compute nodes in platforms

using 1 and 10 GbE links. It comes in 3U VPX VITA 48.2 air- and conduction-cooled rugged versions, equipped with a fully managed or unmanaged switch/router with 24x 1 GbE SERDES ports (IEEE 802.3) and 2x 10 GbE uplink/stacking ports (XAUI). Providing up to 24 wire speed 1,000 Mbps interfaces and up to 2x 10 Gbps interfaces in a single 3U VPX slot, the VPX6-683 is ideal for architecting system-wide Intra-Platform Networks (IPNs). The VPX6-683 FireBlade also features high-performance Layer 2/3+ switching/routing software, along with management ports including Serial RS-232 and in-band GbE. The switch is additionally outfitted with a Rear Transition Module (RTM) with SFPs for 1 GbE and InfiniBand connectors for 10 GbE.

www.cwcembedded.com

**CURTISS-WRIGHT**

### Extended-temp 6U VMEbus CPU

different expansion modules. It utilizes the GMS P70 Nucleus processor module, which supports either the ultra-low power Core 2 Duo operating at 1.5 GHz (L7400 @ 17 W) or the Core 2 Duo at 2.16 GHz (T7400 @ 34 W) with 4 MB of L2 cache and 667 MHz FSB. "Plug-in" configurability is provided, and custom configurations are possible through one PMC-X and/or 16-lane XMC compliant site(s) with rear I/O plus an optional workstation I/O module (second VME site). Meanwhile, I/O comprises three PMC-X sites and/or two eight-lane XMC sites and one PMC-X site; or two Special Application Module (SAM) video modules — one with dual-link DVI-I and one with dual DVI-I to the front panel — and one PMC-X site. Maritime VS275 supports VME 64 and is available in a standard temperature range of 0 °C to +60 °C or an extended temperature range of -40 °C to +85 °C.

www.gms4sbc.com

**GENERAL MICRO SYSTEMS, INC.**

### Low-power, highperformance 6U VME SBC

itech Defense Systems' C160 is an air- or conductioncooled 6U VME SBC featuring the Intel T7500 low-power or high-performance Merom Core 2 Duo dual-core processors. It offers clock frequencies up to

2.2 GHz for the high-performance version and 1.67 GHz for the low-power version, which draws only 25 W. The SBC offers 2eSST and 2eVME functionality as well as VME and PCI legacy support via a Tundra Tsi148 bridge. C160 provides up to 2 GB fast DDR2 SDRAM operating at 667 MHz and up to 8 GB of onboard flash disk (NAND flash) with IDE controller. The SBC also features an integrated GM965 graphics engine with 2D and 3D graphics outputting in either CRT (RGBHV) or composite NTSC, PAL, or RS-170 video formats. It additionally offers two industry-standard PMC sites, two GbE ports, two SATA II interfaces, and two USB 2.0 interfaces, plus legacy interfaces such as two 16C550-compatible RS-232/422/485 serial ports and eight discrete I/O lines.

www.rugged.com

**AITECH DEFENSE SYSTEMS**

# Annapolis Micro Systems The FPGA Systems Performance Leader

# WILDSTAR 5 for IBM Blade The Perfect Blend of Processors and FPGAs

Fully Integrated into IBM Blade Management System

Abundant Power and Cooling Ensure Maximum Performance

Made in the USA

### **Ultimate Modularity**

From 2 to 8 Virtex 5 FPGA/Memory Modules Input / Output Modules Include: Quad 130 MSps thru Quad 500 MSps A/D 1.5 GSps thru 2.2 GSps, Quad 600 MSps A/D Dual 1.5 GSps thru 4.0 GSps D/A Infiniband, 10 G Ethernet, FC4, SFPDP

Direct Seamless Connections with no Data Reduction

Between External Sensors and FPGAs

Between FPGAs and Processors over IB or 10GE Backplane

Between FPGAs and Standard Output Modules

190 Admiral Cochrane Drive, Suite 130, Annapolis, Maryland USA 21401 wfinfo@annapmicro.com (410) 841-2514 www.annapmicro.com

# Cutting it close doesn't cut it

Front card panels require precision. "Close enough" won't make your panel look attractive, keep EMI/RFI contained, or let front I/O components fit flawlessly. That's why Elma cuts its panel corners with a .3 mm radius bit and instills precision into every slice. This attention to detail shows in every panel we produce, whether standard or custom. We take our service seriously too. You'll receive helpful technical support, quotations quickly, and delivery on time, every time. Don't settle for close enough, experience the precision of Elma.

**USA Elma Electronic Inc.**

Phone: 510.656.3400 Fax: 510.656.3783 E-mail: sales@elma.com Web: www.elma.com

### **Custom Panels**

Custom cutouts, silk-screening, and overlays

Assembly of handles, gaskets, and more

Elma's renowned quality and precision

Prototypes to high volumes

Quickturn delivery

### Handles

Industry's largest selection of handle styles

Classic, ergonomic, telco and long-telco styles

Strongest latching button

Patented alignment pin

No longer just a "sea of gates," FPGAs are now used in just about every type of application you can think of, giving COTS designers the ability to solve myriad problems by using the same board in various systems. The solution isn't always a simple one though, as FPGA I/O requirements vary from system to system. However, the VITA 57 (FMC) standard comes to the rescue with its unprecedented mechanical and electrical flexibility. Meanwhile, IP and interoperability are also vital considerations.

Sometimes a design team will see a really nice COTS FPGA board that was just about perfect for their application if only that front panel interface were 12 V instead of 3 V, or round instead of square, blue instead of red, or some similar tweak. Engineers who have experienced this scenario are going to love VITA 57 (FPGA Mezzanine Card or FMC). The reason: VITA 57 provides a standard specification for a small mezzanine module designed to adapt an FPGA-based carrier card to different I/O requirements.

Prior to this standard, most vendors were developing their own proprietary mezzanine boards or redesigning them to fit necessary I/O stipulations - a much more costly equation. However, the FMC specification aims to thwart these costly and time-consuming practices by providing a COTS standard for the industry. However, VITA 57 has its share of plusses and challenges. Primary areas of consideration for FMC use and development include mechanical and electrical details, and FPGA IP - along with the issue of whether you'll really be able to put an FMC from one vendor onto the FMC site of another vendor.

#### Introducing FMC

The FMC is defined as a small add-on module to provide physical-level I/O drivers for carrier cards with FPGAs. (Also see Sidebar 1 for nonstandard uses of FMC.) Carrier form factor support includes VME, VXS, VPX, CompactPCI, and AMC.

### Nonstandard uses and extensions for FMC

While FMC was designed to provide I/O for FPGAs, a nonintended use is to provide additional processing, whether it be another FPGA or a DSP. With 10 W allowed, and more as long as you can cool it, FMCs could be used to enable what are essentially coprocessors for the baseboard FPGA.